| 【FPGA】基于VGA的图像显示 | 您所在的位置:网站首页 › fpga 开发板刷新率 › 【FPGA】基于VGA的图像显示 |

【FPGA】基于VGA的图像显示

|

目录

一丶VGA协议二丶彩条显示1.任务分析2.代码设计

三丶显示名字1.任务分析2.代码设计

四丶图片显示1.任务分析2.代码设计

一丶VGA协议

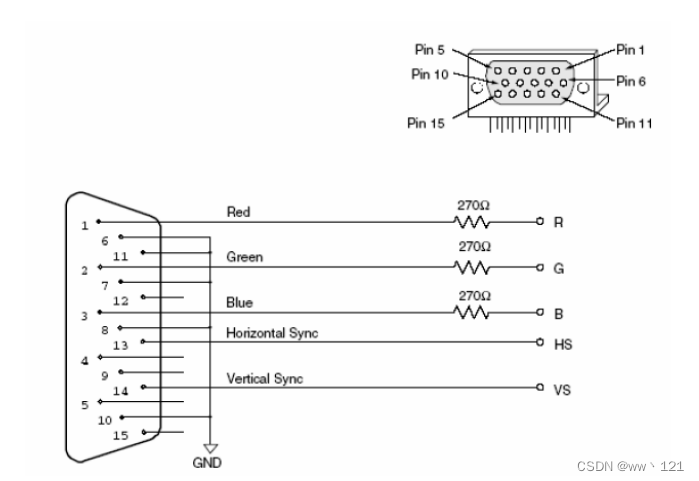

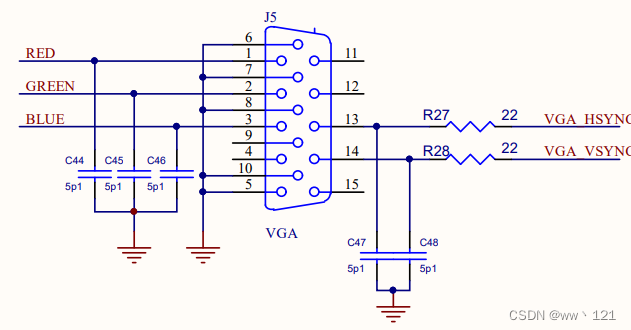

VGA的全称是Video Graphics Array,即视频图形阵列,是一个使用模拟信号进行视频传 输的标准。早期的CRT显示器由于设计制造上的原因,只能接收模拟信号输入,因此计算机内 部的显卡负责进行数模转换,而VGA接口就是显卡上输出模拟信号的接口。如今液晶显示器虽 然可以直接接收数字信号,但是为了兼容显卡上的VGA接口,也大都支持VGA标准。 VGA端口的结构: VGA端口是视频输出端口,端口一共包含15个管脚,如下图:

VGA原理: 在通常使用的连接方法里面,15个管脚里面的5个是最重要的,他们 包括3个基本红,绿,蓝三条基本色彩线和水平与垂直两条控制线

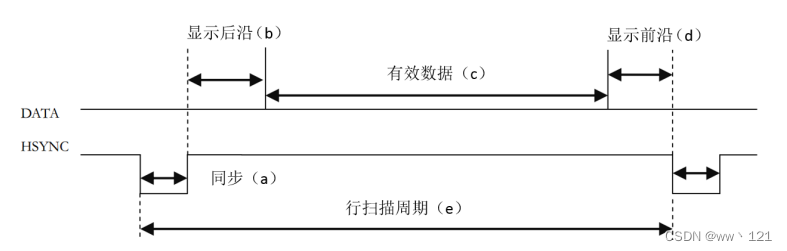

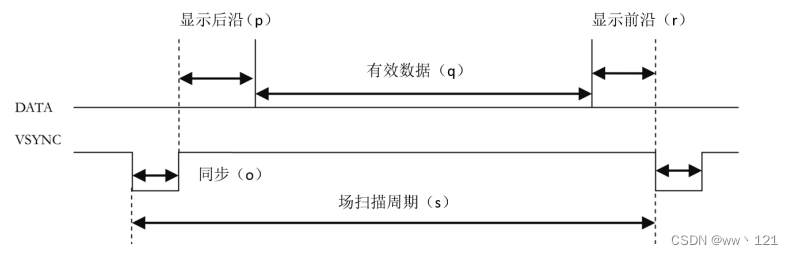

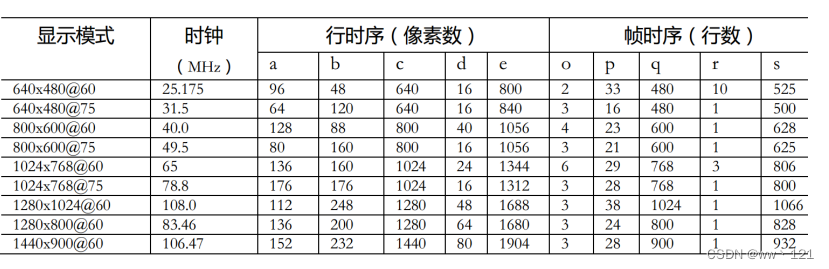

VGA接口标准: VGA工业标准所要求的频率: • 时钟频率: 25.175MHz(像素输出的频率); • 行频: 31469Hz; • 场频: 59.94Hz。 显示器技术规格提供的行频一般在30kHz~45kHz(保守数据),场频一般在 50Hz~75Hz(保守数据),针对以上保守数据,以30kHz的行频进行扫描时 所需时钟频率为:30kHz×800(行周期)=24MHz,则场频为:30kHz÷525( 场周期)=57.14Hz 在VGA视频传输标准中,视频图像被分解为红、绿、蓝三原色信号,经过数模转换之后,在行同步(HSYNC)和场同步(VSYNC)信号的同步下分别在三个独立通道传输。VGA在传输过程中的同步时序分为行时序和场时序 行同步时序: 场同步时序: 从上面两幅图中我们可以看到VGA传输过程中的行同步时序和场同步时序非常类似,一行或一场(又称一帧)数据都分为四个部分:低电平同步脉冲、显示后沿、有效数据段以及显示前沿。 行同步信号HSYNC在一个行扫描周期中完成一行图像的显示,其中在a段维持一段时间的低电平用于数据同步,其余时间拉高;在有效数据期间(c段),红绿蓝三原色数据通道上输出一行图像信号其余时间数据无效。 与之类似,场同步信号在在一个场扫描周期中完成一帧图像的显示,不同的是行扫描周期的基本单位是像素点时钟,即完成一个像素点显示所需要的时间;而场扫描周期的基本单位是完成一行图像显示所需要的时间。 早期的VGA特指分辨率为640X480的显示模式,后来根据分辨率的不同,VGA又分为VGA(640x480)、SVGA(800x600)、XGA(1024x768)、SXGA(1280x1024)等。不同分辨率的VGA显示时序是类似的,仅存在参数上的差异,如图 18.1.5所示。 需要注意的是,即便分辨率相同,刷新速率(每秒钟图像更新次数)不一样时,对应的VGA像素时钟及时序参数也存在差异。例如,显示模式“640480@75”刷新速率为75hz,与相同分辨率下刷新速率为60hz的“640480@60”模式相比,像素时钟更快,其他时序参数也不尽相同。

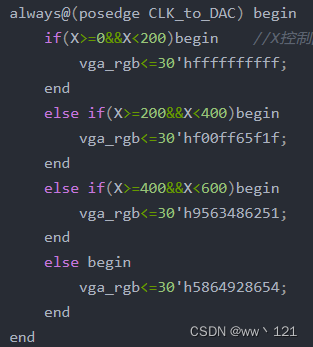

本节实验任务是使用FPGA开发板上的VGA接口在显示器上显示彩条,要求分辨率为 640*480,刷新速率为60hz。

此部分实现彩条显示只需要给像素横坐标设置范围,在规定范围显示对应的颜色即可 |

【本文地址】